Overview

Audio processing is very important for consumer electronics applications such as mobile phones and tablets, and other mass-produced products. Area and power consumption are often key design criteria, and the market requires high-quality, high-fidelity (Hi-Fi) audio. Integrating silicon-proven and optimized audio IP for specific audio functions helps reduce power, area and cost of today's multimedia chip systems.

As designs gradually transition to 28-nm process technology, the challenge of integrating audio functions becomes more complex because analog circuits do not follow Moore's Law and do not scale down as processes evolve. Wafer costs using the 28nm process will be much higher than 65nm or 40nm process technology. Digital circuits follow Moore's Law, and while wafer costs increase, their performance and density increase. The analog circuit used in the audio codec generally uses IO devices, so it does not use a core device like a digital circuit to reduce the size. As the cost of the wafer increases, the inherent performance of the analog circuit does not improve and the area does not decrease. Therefore, a new architecture must be developed to reduce the total area. For example, an audio codec with an area of ​​2.5 square millimeters using 65 nanometer technology, with 28 mm technology, needs to be reduced to 1.9 square millimeters to keep silicon costs the same. It is this 25% reduction in area that constitutes a key challenge for advanced process node audio codecs.

This paper examines the major system and technical challenges of integrating audio functionality into 28nm mobile multimedia chip systems and how to address these challenges through the following technologies:

· Use Moore's Law to change some functions from analog to digital;

Flexible design to support the audio sampling rate of the chip system's universal reference clock;

· Do a good balance between power supply voltage reduction and performance;

· Gain insight into the division of system functions outside the chip system;

Recognizing that there are steps to minimize system cost, designers and system architects will be able to find an effective balance between cost, functionality and performance, enabling them to embed audio IP decoder solutions to help their SOC compete Win.

Audio codec basics

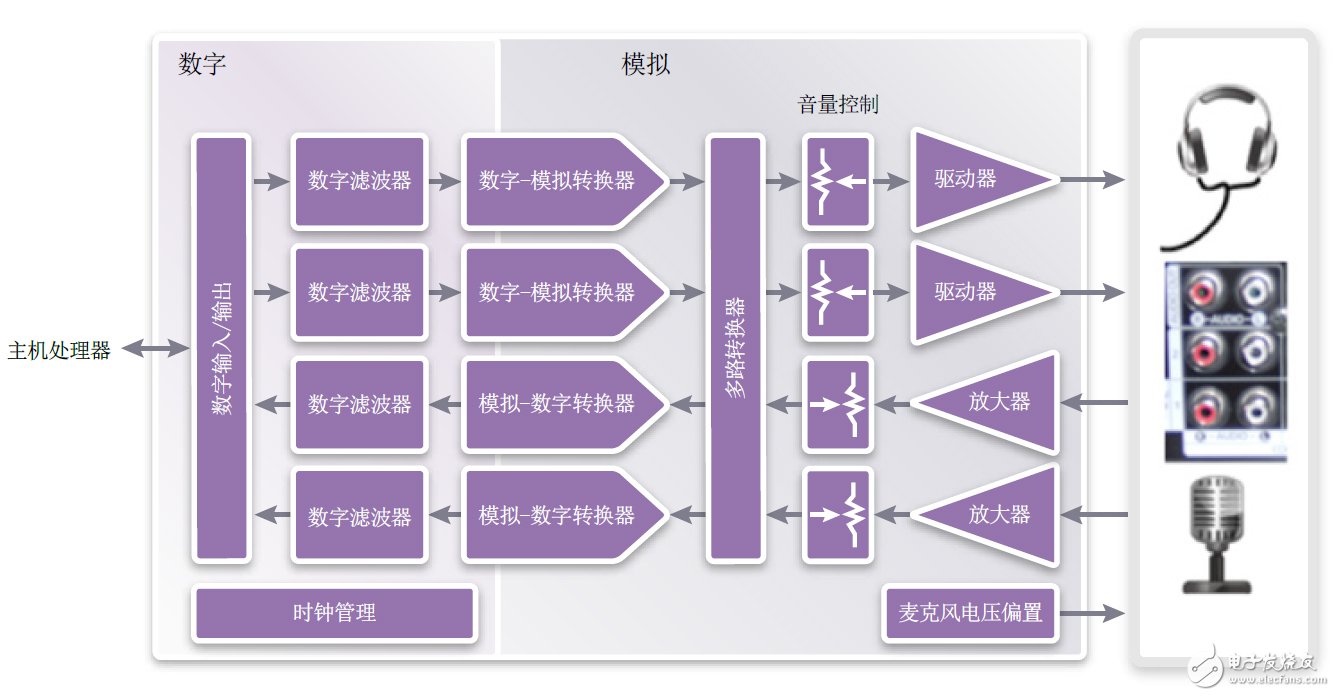

The audio codec is mainly composed of two types of data converter modules, namely an analog-to-digital converter (ADC) for recording and a digital-to-analog converter (DAC) for playback. For stereo or multi-channel decoders, these modules are copied separately. Figure 1 is a block diagram of a typical stereo audio codec. The Chinese recording channel includes an amplifier with volume control that adjusts the small signal microphone and large signal cable to the input range of the analog-to-digital converter. The playback channel includes the ability to directly drive the headphones or small speaker amplification, each with a volume control function. There is also a low noise power supply that provides a microphone bias.

The digital circuit has multiple components, the most important of which is the digital audio filter, which converts the data rate into an over-sampling clock of the data converter and eliminates high-frequency noise outside the audio band. Clock management is also important to ensure that modules at different rates are synchronized with each other and support multiple sample rates.

Figure 1: Functional block diagram of the audio codec

Road Light,Double Arms Road Light,Off Road Lights,Round Road Light

Yangzhou Heli Photoelectric Co., Ltd. , https://www.heli-eee.com