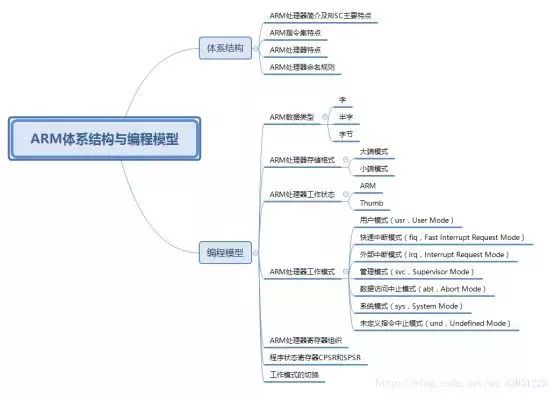

ARM processor introduction and RISC features

Introduction to the First ARM Processor and RISC Features

The ARM processor is a widely used 32-bit RISC (Reduced Instruction Set Computing) architecture that has become a cornerstone in embedded systems. Designed for efficiency, low power consumption, and high performance, ARM processors are found in everything from smartphones to industrial control systems. The RISC philosophy emphasizes simplicity and speed by reducing the number of instructions and making them more uniform.

Key Features of RISC Design

1. **Instruction Set**: RISC architectures simplify the instruction set, allowing one instruction per clock cycle. Instructions are typically fixed-length, which makes decoding faster and more efficient. This contrasts with CISC (Complex Instruction Set Computing), where instructions can vary in length and complexity.

2. **Pipeline Architecture**: RISC processors benefit from pipelining due to their fixed instruction format. Each stage of the pipeline can be executed in parallel, significantly improving throughput and execution speed.

3. **Registers**: RISC designs often include a large number of general-purpose registers. For example, the ARM architecture provides up to 37 registers, including 16 general-purpose registers and several special-purpose ones, enhancing performance by reducing memory access.

4. **Load/Store Structure**: Unlike CISC, which allows direct memory access in many instructions, RISC uses dedicated load and store instructions to move data between memory and registers. This simplifies the instruction set and improves efficiency.

5. **Simplified Addressing Modes**: RISC reduces the number of addressing modes, making the instruction format more consistent and easier to decode.

ARM Instruction Set Features

While based on RISC principles, the ARM instruction set includes some enhancements tailored for embedded systems. These features make it more versatile and efficient than a pure RISC design:

1. **Variable Instruction Cycles**: Some instructions, like multi-register load/store operations, have variable cycle counts depending on the number of registers involved. This flexibility helps optimize performance for specific tasks.

2. **Barrel Shifter**: ARM incorporates a hardware barrel shifter that allows complex shifts to be performed in a single cycle. This enhances the functionality of many instructions without increasing the instruction count.

3. **Thumb Instruction Set**: To improve code density, ARM supports a 16-bit Thumb instruction set alongside its 32-bit ARM instructions. This dual-mode approach allows developers to choose between performance and compactness as needed.

4. **Conditional Execution**: Many ARM instructions can be conditionally executed based on the state of the CPSR flags. This reduces the need for branch instructions, leading to better performance and smaller code size.

5. **Enhanced Instructions**: ARM also includes DSP-like instructions for operations such as 16×16 multiplication and saturation, making it suitable for signal processing tasks without requiring a separate DSP core.

Core Features of the ARM Processor

1. Fixed 32-bit instruction length

2. Large register file (up to 37 registers)

3. Load/Store architecture

4. Multiple register load/store support

5. Conditional execution of instructions

6. Single-cycle data shift and ALU operations

7. Extensibility through coprocessors and variants

8. Support for the 16-bit Thumb instruction set

ARM Processor Naming Rules and Programming Model

In the ARM architecture, data units are defined as follows:

- **Word**: 32 bits

- **Half-word**: 16 bits

- **Byte**: 8 bits

Memory in ARM is treated as a linear sequence of bytes starting at address zero. It supports a maximum of 4GB of address space. Data can be stored in either big-endian or little-endian format:

- **Big-endian**: The most significant byte is stored at the lowest address.

- **Little-endian**: The least significant byte is stored at the lowest address.

ARM Processors operate in two main states:

1. **ARM State**: Executes 32-bit instructions aligned on word boundaries.

2. **Thumb State**: Executes 16-bit instructions aligned on half-word boundaries.

Working Modes of the ARM Processor

The ARM processor has several operating modes, including:

- **User Mode (usr)**: Normal program execution mode.

- **Fast Interrupt Request (FIQ)**: Used for high-speed data transfer.

- **Interrupt Request (IRQ)**: General-purpose interrupt handling.

- **Supervisor Mode (svc)**: System-level protection mode.

- **Abort Mode (abt)**: Handles memory access errors.

- **System Mode (sys)**: Privileged mode for system tasks.

- **Undefined Mode (und)**: Handles undefined instructions.

Most of these modes are privileged, except for User and System modes. In privileged modes, programs can access all system resources, while user mode requires switching to privileged mode for hardware access.

Register Organization

The ARM processor contains 37 32-bit registers, including 31 general-purpose registers and 6 status registers. These include:

- R0-R15 (general-purpose registers)

- R8_fiq-R14_fiq (FIQ mode registers)

- R13_svc, R14_svc (Supervisor mode registers)

- R13_abt, R14_abt (Abort mode registers)

- R13_irq, R14_irq (IRQ mode registers)

- R13_und, R14_und (Undefined mode registers)

- CPSR (Current Program Status Register)

- SPSR (Saved Program Status Register)

General-purpose registers are divided into ungrouped (R0-R7), grouped (R8-R14), and the program counter (R15). The CPSR holds the current status flags, including N (Negative), Z (Zero), C (Carry), V (Overflow), I (Interrupt Disable), F (Fast Interrupt Disable), T (Thumb mode), and M (Mode bits).

Switching Between Modes

Mode switching occurs through various triggers, such as SWI instructions, interrupts, or exceptions. For example, an SWI in user mode switches to Supervisor mode, while an external interrupt may trigger IRQ or FIQ mode. Exceptions like data aborts or undefined instructions switch to Abort or Undefined mode, respectively. System mode must be manually entered by changing the CPSR mode bit.

Shaanxi Xinlong Metal Electro-mechanical Co., Ltd. , https://www.cnxlalloys.com